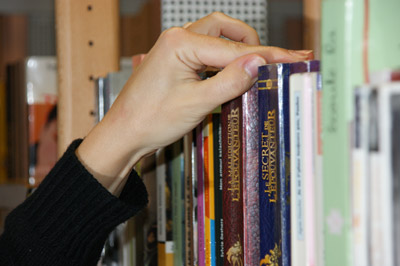

| Titre : | Application-specific integrated circuits | | Type de document : | texte imprimÃĐ | | Auteurs : | Michael John Sebastian Smith, Auteur | | Editeur : | Menlo Park, California; Harlow,England; Tokyo : Addison-Wesley | | AnnÃĐe de publication : | 1997 | | Collection : | VLSI Systems Series | | Importance : | 1026 p. | | PrÃĐsentation : | couv. ill.,ill. | | Format : | 23,2 cm. | | ISBN/ISSN/EAN : | 978-0-321-60275-6 | | Langues : | Anglais (eng) | | Index. dÃĐcimale : | 27-05 Microélectronique | | RÃĐsumÃĐ : | This comprehensive book on application-specific integrated circuits (ASICs) describes the latest methods in VLSI-systems design. ASIC design, using commercial tools and predesigned cell libraries, is the fastest, most cost-effective, and least error-prone method of IC design. As a consequence, ASICs and ASIC-design methods have become increasingly popular in industry for a wide range of applications. The book covers both semicustom and programmable ASIC types. After describing the fundamentals of digital logic design and the physical features of each ASIC type, the book turns to ASIC logic design-design entry, logic synthesis, simulation, and test-and then to physical design-partitioning, floorplanning, placement, and routing. You will find here, in practical, well-explained detail, everything you need to know to understand the design of an ASIC, and everything you must do to begin and to complete your own design. | | Note de contenu : | Contents

1. Introduction to ASICs

2. CMOS Logic.

3. ASIC Library Design.

4. Programmable ASICs.

5. Programmable ASIC Logic Cells.

6. Programmable ASIC I/O Cells.

7. Programmable ASIC Interconnect.

8. Programmable ASIC Design Software.

9. Low-Level Design Entry.

10. VHDL.

11. Verilog HDL.

12. Logic Synthesis.

13. Simulation.

-The Different Types of Simulation.

-Structural Simulation.

-Gate-Level Simulation.

-How Logic Simulation Works.

-VHDL Simulation Cycle.

-SDF in Simulation.

- Switch-Level Simulation.

-Transistor-Level Simulation.

-A PSpice Example.

-SPICE Models.

14. Test.

15. ASIC Construction.

16. Floorplanning and Placement.

17. Routing.

Appendix A. VHDL Resources.

Appendix B. Verilog HDLResources.

-Index |

Application-specific integrated circuits [texte imprimÃĐ] / Michael John Sebastian Smith, Auteur . - Menlo Park, California; Harlow,England; Tokyo : Addison-Wesley, 1997 . - 1026 p. : couv. ill.,ill. ; 23,2 cm.. - ( VLSI Systems Series) . ISBN : 978-0-321-60275-6 Langues : Anglais ( eng) | Index. dÃĐcimale : | 27-05 Microélectronique | | RÃĐsumÃĐ : | This comprehensive book on application-specific integrated circuits (ASICs) describes the latest methods in VLSI-systems design. ASIC design, using commercial tools and predesigned cell libraries, is the fastest, most cost-effective, and least error-prone method of IC design. As a consequence, ASICs and ASIC-design methods have become increasingly popular in industry for a wide range of applications. The book covers both semicustom and programmable ASIC types. After describing the fundamentals of digital logic design and the physical features of each ASIC type, the book turns to ASIC logic design-design entry, logic synthesis, simulation, and test-and then to physical design-partitioning, floorplanning, placement, and routing. You will find here, in practical, well-explained detail, everything you need to know to understand the design of an ASIC, and everything you must do to begin and to complete your own design. | | Note de contenu : | Contents

1. Introduction to ASICs

2. CMOS Logic.

3. ASIC Library Design.

4. Programmable ASICs.

5. Programmable ASIC Logic Cells.

6. Programmable ASIC I/O Cells.

7. Programmable ASIC Interconnect.

8. Programmable ASIC Design Software.

9. Low-Level Design Entry.

10. VHDL.

11. Verilog HDL.

12. Logic Synthesis.

13. Simulation.

-The Different Types of Simulation.

-Structural Simulation.

-Gate-Level Simulation.

-How Logic Simulation Works.

-VHDL Simulation Cycle.

-SDF in Simulation.

- Switch-Level Simulation.

-Transistor-Level Simulation.

-A PSpice Example.

-SPICE Models.

14. Test.

15. ASIC Construction.

16. Floorplanning and Placement.

17. Routing.

Appendix A. VHDL Resources.

Appendix B. Verilog HDLResources.

-Index |

|  |

Affiner la recherche Interroger des sources externes

Affiner la recherche Interroger des sources externesApplication-specific integrated circuits / Michael John Sebastian Smith